Members approve interface spec that could act as a catalyst for chip developments

June 10, 2002

What could turn out to be a milestone in the development of 40-Gbit/s transport equipment is about to be announced by the Optical Internetworking Forum (OIF).

The achievement -- the result of a ballot of OIF members concerning its so-called SerDes-Framer Interface 5 (SFI-5) -- may sound a little arcane. But it paves the way for system vendors to mix and match chips from different suppliers in their 40-gig systems; and that promises to encourage semiconductor manufacturers to charge ahead with developments, knowing there's a free and open market for their 40-gig products.

"It takes the risk away," says Tom Palkert, a member of the board of the OIF and a systems architect with Applied Micro Circuits Corp. (AMCC) (Nasdaq: AMCC). "Whether the market is there is another matter," he cautions.

Some vendors have already developed products based on the SFI-5 spec, on the assumption that it would gain the approval of OIF members in last week's ballot.

Agilent Technologies Inc. (NYSE: A), for instance, already has a tester for evaluating SFI-5 interfaces. The so-called ParBERT (Parallel Bit Error Rate Tester) measures the way in which the 40 Gbit/s of traffic is split into 16 channels, each running at 2.5 Gbit/s, and synchronized using two extra channels of signaling info.

"The SFI-5 interface is a key specification for the creation of industry standard 40G transponders," writes Larry Desjardin, Agilent's high-bandwidth program manager, in an email to Light Reading. "This will help the economies of scale, a key success factor for 40G."

Agere Systems (NYSE: AGR) "has multiple devices currently in development that will support SFI-5," writes Glen Haley, Agere's media relations manager, in another email. "Agere absolutely believes that the OIF SFI-5 interface will be very relevant to next-generation solutions for multiport 10G applications that become migrateable to OC768C applications."

Not everybody agrees that SFI-5 will be important, however. Bill Woodruff, vice president of marketing for Velio Communications Inc., sees only "very narrow applications" for it. One of his reasons for saying this is that most system vendors won't want to use a standardized FEC (forward error correction) chip, in his opinion, because proprietary FEC technologies have far better performance. "People kill for a half decibel in this business," he hyperbolizes.

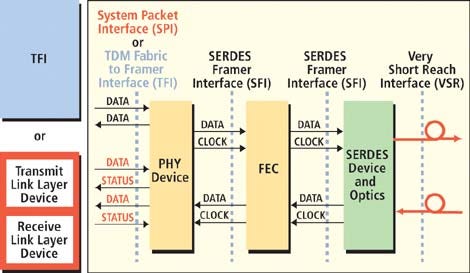

To put things in perspective, the OIF is standardizing four interfaces between the chips found in a typical transponder. . The current status is as follows:

. The current status is as follows:

Very Short Reach (VSR) interfaces, between SerDes and optical devices, have already been standardized (see OIF Promotes VSR Specs).

SerDes Framer Interface (SFI), between SerDes and framer (FEC or PHY) chips: The OIF has already standardized a 10-Gbit/s version, called SFI-4 and is working on a more compact version called SFI-4, Phase 2. Now it's settled on a 40-Gbit/s version called SFI-5.

System Packet Interface (SPI), between network processors and framer chips: Standards already exist for a 10-Gbit/s version, SPI-4, and a compact 10 Gbit/s version, SPI-4 Phase 2.

TDM Fabric-to-Framer Interface, between switches and framer chips, is still a work in progress.

— Peter Heywood, Founding Editor, Light Reading

http://www.lightreading.com

You May Also Like